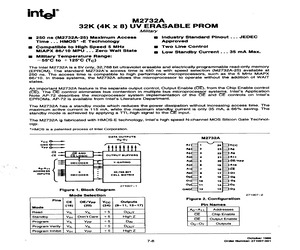

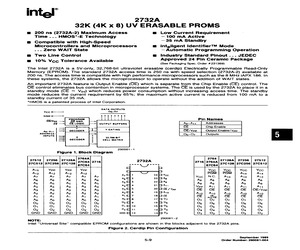

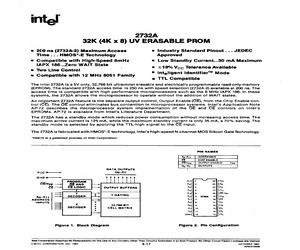

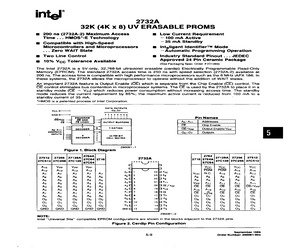

2732A-25) Maximum Access a Industry Standard Pinout ... JEDEC Time ... HMOS* -E Technology Approved w Compatible to High Speed 5 MHz w Two Line Control MiAPX 86/10 MPU ... Zero Wait State w Low Standby Current... 35 mA Max. w Military Temperature Range: 55C to + 125C (Tc) The Intel M2732A is a 5V only, 32,768 bit ultraviolet erasable and electrically programmable read-only memory (EPROM). The standard M2732As access time is 450 ns with speed selection (M2732A-25) available at 250 ns. The access time is compatible to high performance microprocessors, such as the 5 MHz MiAPX 86/10. In these systems, the M2732A allows the microprocessor to operate without the addition of WAIT states. An important M2732A feature is the separate output control, Output Enable (OE), from the Chip Enable control (GE). The OE control eliminates bus contention in multipte bus microprocessor systems. Intel's Application Note AP-72 describes the microprocessor system implementation of the OE and CE controls on I

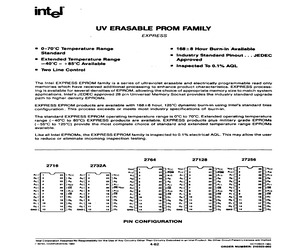

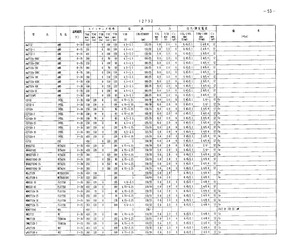

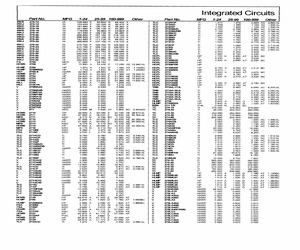

16 2048x8 450 5V = 5% -40 to 85 NONE QD2732A-2 4096x8 200 5V + 5% 0 to 70 168+8 QD2732A 4096x8 250 5V + 5% 0 to 70 168+8 QD2732A-3 . 4096x8 300 5V + 5% 0 to 70 1688 Q0D2732A-4 4096x8 450 5V + 5% 0 to 70 168+8 QD2732A-20 4096x8 200 5V + 10% - Qto 70 1688 QD2732A-25 4096x8 250 SV + 10% 0 to 70 168+8 QD2732A-30 4096x8 300 5V + 10% 0 to 70 168+8 LD2732A 4096x8 250 5V = 5% ~40 to 85 168+8 LD2732A-4 4096x8 450 5V + 5% ~40 to 85 168+8 L02732A-25 4096x8 250 5V + 10% - 40 to 85 168+8 LD2732A-45 4096x8 450 5V + 10% -40 to 85 168+8 1D2732A 4096x8 250 5V + 5% -40 to 85 NONE TO2732A-4 4096x8 450 5V + 5% -40 to 85 NONE T02732A-25 4096x8 250 5V + 10% -40 to 85 NONE TD2732A-45 4096x8 450 5V + 10% ~40 to 85 NONE QD2764-2 8192x8 200 5V + 5% 0 to 70 168+8 Q02764 8192x8 250 5V = 5% 0 to 70 16828 QD2764-3 8192x8 300 5V + 5% 0 to 70 168+8 QD2764-4 8192x8 450 5V + 5% 0 to 70 168+8 QD2764-25 8192x8 250 5V + 10% 0 to 70 168+8 QD2764-30 8192x8 300 5V + 10% 0 to 70 168+8 QD2764-45 8192x8 450 5V +

D63PA05YO 1ID63PB05YO DC-64SP DC-64SP HD63P05Yl DC-64SP - 1ID63PA05Yl 1ID63PB05Yl DC-64SP DC-64SP 1ID6305XO 1ID63A05XO 1ID63B05XO 1ID6305Xl 1ID63A05Xl 1ID63B05Xl 1ID6305YO 1ID63A05YO 1ID63B05YO 1ID6305Yl 1ID63A05Yl 1ID63B05Yl HN482732A-30 HN482732A-30 HN482732A-25 Device 4 k bytes EPROM HN482732A-30 HN4827 32A- 30 HN482732A-25 HN482764-3 HN482764-3 HN482764 HN482764-3 HN482764-3 HN482764 HN27C64-30 HN27C64-30 HN27C64-25 HN27C64-30 HN27C64-30 HN27C64-25 8 k bytes '- - Accumul.tor * A D. Index Port A Register x I/O Terminels Condition 5 Code Regis ** r CCA ""lIlT;" D. Port 0 ~; 'nput Terminels OJ D, ... , Pan B I/O " '." '.' Terminels ... """ " '.'. '.'. Pan E Output Terminels Port F Output Terminels Seriel Control Register to a=~er PanG I/O Terminels Port A I/O Terminals Condition Code Register CCR 0, 0, INT2 0, D. Port 0 0, Input 0, Terminals 0, Stack Port B I/O Pointer Sp Program Counter "High" PCH Program Counter "Low" Terminals ADRu AOR12 ADR" ADR,o PCl ADR, ADA. ADR, ADR, ADRs AD

32-1 AND | ox70| 350 of 360[ too] 455.5 150/30| 0.8) 20) 6{ 0.45/21 2.4/0.4| 12 | An2732-2 AMD o~70 | 450 of 450] 100) 45455 150/30] 0.8] 20| 6] 0.45/21 2.4/0.4] 12 | An27 324-2006 AND o~70 | 200 of mo] so) 45~55 100725] 0.8| 20] 6] 0.45/21 2.4/0.4| 12 | n2732A-250C AMD o~70 | 250 [oj wo! so) 45~55 1o025| 08] 20] 6| 0.45/21 2.4/0.4) 12 | An2732A-206 AMD o~70 | 200 of 70] 60] 45~55 100/25 { 0. = 0. 45/2.1 24/0.4| 12 _ An2732A-300C AND o~70 | 300 o[ iso) 130, 45~5.5 10/25 0.8] 20] 6[ 0.45/21 2.4/0.4 12 An27324-30C AMD o~70 | 300 of iso} 10. 45455 woes{ 08] 20] 6| 045/21 2.4/0.4] 12 | An2792A-45D AND a~70 | 450 of iso] 130[ 45455 1072s; 0.8] 20] 6| 0.45/21 2.4/0.4] 12 _| An2732A-ADC AND t~70 | 450 a| 190] 190) 4.5~5.5 100/25] oa] 20, 6{ 0.45/21 rl a An2732A-DC AMD o~70 [250 of tof so; 45~5.5 wov25{ as] 20] 6{ 045/21 247.4{ 12 | AmZ7I2APC AMD o~70 [250 of] wo] sof 45~5.5 100/25] 08] 20/ 6] 0.45/21 24/04] 12 62732 INTEL o~70] 450} 120[ 0 100] 4. 75~5. 25 150/30, 08) 20] 6| 0.45/21 2.4/-|_12| Ce c2732-

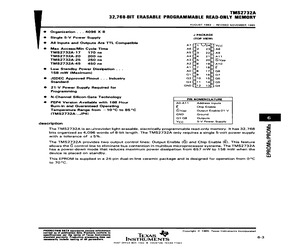

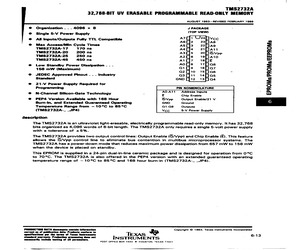

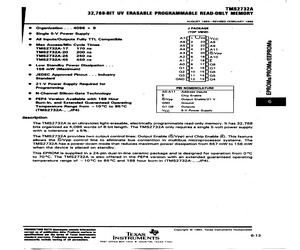

2732A-25 250 ns TMS2732A-45 450 ns @ Low Standby Power Dissipation . . . 158 mW (Maximum) @ JEDEC Approved Pinout . . . Industry Standard @ 21-V Power Supply Required for Programming AUGUST 1983 REVISED NOVEMBER 19385 J PACKAGE (TOP VIEW) 471 U2 vec a6 []2 73H ae 453 220] a9 aoe aitjait a3 (5 79H Sivee A2[}s is{} aro aifi7 islje& aos 17[C)a8 ai[j9 16[Ja7 o2[i0 15[ Jas o3(]11 140 05 Gno(ji2 13f} a4 @ N-Channel Silicon-Gate Technology PIN NOMENCLATURE @ PEP4 Version Available with 168 Hour AO-A11 Burn-in and Guaranteed Operating E Temperature Range from 10C to 85C G/Vpp (TMS2732A-__JP4) GND 21-08 description Vee Address Inputs Chip Enable Output Enable/21 V Ground Outputs 5-V Power Supply The TMS2732A is an ultraviolet light-erasable, electrically programmable read-only memory. It has 32,768 bits organized as 4,096 words of 8-bit length. The TMS2732A only requires a single 5-volt power supply with a tolerance of +5%. The TMS2732A provides two output control lines: Output Enable (G) and Chip Enable

2732A-25 250 ns TMS2732A-45 450 ns All Inputs/Outputs Fuly TTL Compatible @ Low Standby Power Dissipation .. . 158 mW (Maximum) @ JEDEC Approved Pinout... Standard @ 21-V Power Supply Required for Programming @ N-Channel Silicon-Gate Technology @ PEP4 Version Available with 168 Hour Burn-in, and Extended Guaranteed Operating Temperature Range from 10C to 85C (TMS2732A-_ _JP4) description Industry AUGUST 1983REVISED FEBRUARY 1988 J PACKAGE (TOP VIEW) A7(]1 V2aQ vec A6qj2 230s as(j3 22Djag A4f]4 21f}ait A3(]5 20f]G/vpp A2(]6 Bia AiQ77 18DE Aot}s 1708 aifj9 16fja7 Q2[j10 15)[Ja6 o3{]11 14705 GND (J12 130} 04 PIN NOMENCLATURE A0-A11 E Gvpp GND Q1-08 Vec Address Inputs Chip Enable Output Enable/21 V Ground Outputs 5-V Power Supply EPROMs/PROMs/EEPROMs The TMS2732A is an ultraviolet light-erasable, electrically programmable read-only memory. it has 32,768 bits organized as 4,096 words of 8-bit length. The TMS2732A only requires a single 5-volt power supply with a tolerance of +5%. The TMS2732A provides

2732A-25 250 ns TMS2732A-45 450 ns All Inputs/Outputs Fuly TTL Compatible @ Low Standby Power Dissipation .. . 158 mW (Maximum) @ JEDEC Approved Pinout... Standard @ 21-V Power Supply Required for Programming @ N-Channel Silicon-Gate Technology @ PEP4 Version Available with 168 Hour Burn-in, and Extended Guaranteed Operating Temperature Range from 10C to 85C (TMS2732A-_ _JP4) description Industry AUGUST 1983REVISED FEBRUARY 1988 J PACKAGE (TOP VIEW) A7(]1 V2aQ vec A6qj2 230s as(j3 22Djag A4f]4 21f}ait A3(]5 20f]G/vpp A2(]6 Bia AiQ77 18DE Aot}s 1708 aifj9 16fja7 Q2[j10 15)[Ja6 o3{]11 14705 GND (J12 130} 04 PIN NOMENCLATURE A0-A11 E Gvpp GND Q1-08 Vec Address Inputs Chip Enable Output Enable/21 V Ground Outputs 5-V Power Supply EPROMs/PROMs/EEPROMs The TMS2732A is an ultraviolet light-erasable, electrically programmable read-only memory. it has 32,768 bits organized as 4,096 words of 8-bit length. The TMS2732A only requires a single 5-volt power supply with a tolerance of +5%. The TMS2732A provides

70 125 mA Vit Input low voltage -0.1 +0.8 Vv ViH Input high voltage 2.0 Vec+ 1 Vv VoL Output Low voltage lo. = 2.1 mA 0.45 Vv Vou Output high voltage loH = -400 pA 2.4 Vv AC CHARACTERISTICS 2732A-2 2732A 2732A-3 2732A-4 Symbol Parameter Covttion 2732A-20 2732A-25 2732A-30 2732A-45 Unit Min | Max | Min | Max | Min | Max | Min | Max taco | Address to Output | CE_GE=Vvi. 200 250 300 450 | ns Delay tce CE to Output delay | OE=Vit 200 250 300 450 ns tor OE to Output Delay! CE=ViL 100 100 150 150 ns tor) | OF High to Output SEV se | o 6 o | 130 | 0 | 130 ns Output hold from__ address, CE or OE | ae_ae_ toH | Whichever occured | CE=OE=Vin 0 0 0 ns first CAPACITANCE (Tams = 25C, f = 1 MHz) Symbol! Parameter Test Condition Min Typ Max Unit Input Capacitance except _ Cin OEVer Vin = OV 4 6 pF Cine OE/Vpe Input Capacitance Vin = OV , 20 pF Court Output Capacitance Vout = OV 8 12 pF NOTES : 1. Vcc must be applied simultaneously or before Ver and removed simultaneously or after Vpp. 2. Vpp may be connected d

CE = Vit Vit Input Low Voltage 0.1 0.8 Vv Vin Input High Voltage 2.0 Voc + 1 Vv VoL Output Low Voltage 0.45 Vv lop = 2.1MA VoH Output High Voltage 2.4 Vv lon = 400 pA A.C. CHARACTERISTICS 0C < Ta < 70C Versions Voc +5% 2732A-2 2732A Test Vec 10% 2732A-20 2732A-25 Units Conditions Symbol Parameter Min Max | Min | Max tacc Address to Output Delay 200 250 ns CE = OF = Vi toe CE to Output Delay - 200 250 ns OE = ViL toe OE/Vpp to Output Delay 70 100 ns CE = Vit tor (4) OE/Vpp High to Output Float 60 60 ns CE = Vit tou{4) Output Hold from Addresses, 0 ns CE = OE = Vi CE or OE/Vpp, Whichever Occurred First NOTES: 1. Voc must be applied simultaneously or before OE/Vpp and removed simultaneously or after OE/Vpp. 2. The maximum current value is with outputs Og to O7 unloaded. 3. Typical values are for Ta = 25C and nominal supply voltages. 4. This parameter is only sampled and is not 100% tested. Output Float is defined as the point where data is no longer drivensee timing diagram.intel 2732A CAPACITANCE

@o0 ns 300 ns 2732 A-2 (Intel), GD 2732 A-2 (In- tel), MBM 2732A -20 (Fujitsu), 2732 Aw20 (Intel) . MBM 2732A =25 (Fujitsu), 2732 A (Intel), 2732 Au25 (Intel), MCM 2532-25 (Motorola), MCM 25L32~ 25 (Motorola), TMM2732 -2 (Toshi- ba), QD 2732 A (Intel), QD 2732A-25 (Intel), LO 2732 A (Intel), LO 2732A25 (Intel), TO 2732 A (Intel), TD 2632As25 (Intel) MBM 2732A +30 (Fujitsu), MBM 2732A =30X (Fujitsu), 2742A= 30 (Intel), 2732 A-30 (Intel), QD 2732A- 3 (Intel), QO 2732 A30 (Intel), M 58735 (Mitsubishi) U 2732 C35 J 2732 C45 UY 2732 G55 450 ns ' F 2732 (Fairchild), HN 462532 AM 2732 (AMD), AM 2732 M (AMD), (Hitachi), HN 46 2732 (Hitachi), 2732A #4 (Intel), M 2732 A (Intel) M 5L2732 (Mitsubishi), MCM 2532 (Motorola) MCM 25L32 (Motorola), NMC 2532 (National), NMC 27C32- 45 (National), puro 2732 (NEC= Micro), : MSM 2732 (OKI), TMM 2732 (Toshiba), QD 2732A =4 (Intel), LD 2732A -4 (Intel), LD 2732A -45 (Intel), TD 2732A -4 (Intel), TD 2732A -45 (Intel) U 2732 C45 U 2732 C55 550 ns M 2732 (Intel), S 8416 (I

C64 = TYPE OF PRODUCTS HD63P0570, HD63PA05Y0, HD63PB05Y0 (DC-645P) 8 PIN ARRANGEMENT Type No. Bus Timing Applied EPROM HD63P05Y0 1 MHz HN482732A-30, HN482764-3, HN27C64-30 HD63PAQ05Y0 | 1.5 MHz | HN482732A-30, HN482764-3, HN27C64-30 HD63PBOSY0 | 2 MHz HN482732A-25, HN482764, HN27C64-25 (Note) EPROM is not attached to the MCU, @ PROGRAM DEVELOPMENT SUPPORT TOOLS @ Cross assembier software for use with IBM PCs and compat- ibles @ Incircuit emulator for use with IBM PCs and compatibles (Top View) @ HITACHI Hitachi America, Ltd. Hitachi Piaza 2000 Sierra Point Pkwy. Brisbane, CA 94005-1819 (415) 589-8300 571HD63P05Y0, HD63PA05Y0, HD63PBO5Y0 = BLOCK DIAGRAM > TIMER Prescaler Timer/ & Counter Timer control ya Port A HO Terminals Port B ie) Terminals Port C 40 Terminats Clk t- C)<+ C- C,.+__ Port A Register Data Direc- tion Register XTAL EXTAL ORES NUM Oscillator 1 int Accumulator A FE index Register cPu Control x Condition Cade Register cc Stack Pointer cru SP Port B Register Data Direc- tion Register

ge ~0.1 0.8 v Vin input High Voltage 2.0 Voc +1 Vv Vor Output Low Voltage 0.45 Vi] lop = 2.1 mA Vou Output High Voitage 2.4 Vv lon = 400 pA Vpp" Vpp Read Voltage 3.8 Veco V_ | Vog=5.0V+ 0.25V A.C. CHARACTERISTICS 2732A-2 2732A 2732A-3 | 27304-4 2732A-20 | 2732A-25 | 2732A-30 Test Symbol Parameter Min. | Max.| Min.| Max. | Min. | Max. | Min.| Max. | Units| Conditionst tacc Address to Output Delay 200 250 300 450 | ns |CE= OE =Vy. toe CE to Output Delay 200 250 300 460 | ns |OE=Vy,- toe OE to Output Delay 70 100 150 150 | ns |CE=Vy, tor!4l | OE High to Output Not Driven 60 60 130 | oO | 130 | ns |CE=VYy tou Output Hold from Addresses, 0 ns | CE = OF = Vit CE or OE Whichever Occurred First tA.C. TEST CONDITIONS Output Load .............: + TTL gate a and C, = 100 pF Timing Measurement Reference Level: Input Rise and Fall Times ...............5...50. < 20ns Inputs ............--..05. pet eeeeneeeee 0.8 and 2.0V Input Pulse Levels ................-....5- 0.45V to 2.4V Outputs ...... 0... eee eee ee 0.

270ZS05 270ZT05 271 HARR HARR HARR HARR HARR HARR HARR HARR HARR NSC 0.400 0.350 0.420 2.660 3 660 2.350 0.300 0.340 0.340 0.600 M 0.400 0.350 0.420 2.660 3.660 2,350 0.300 0.340 0.340 0.600 AY TIVIS TIVIS TIVIS TIVIS TIVIS HLNP HLNP EISN IC IC 2732A-20JL 2732A-25.1L 2732A-30JL 2732A-35JL 2732A-45JL 2735 2735#S02 274 T/R 274-10 274-20 TI TI TI TI TI HP HP PHIL TI TI 7.220 6.660 6.110 5.770 5550 2.240 A 2450 A 0.548 N 376.000 26.000 7.220 5.430 AC 6.660 5.010 AC 6.110 4.590 AC 5.770 4.340 AC 5.550 4,180 AC 1,920 ID 1.760 AT 2.090 D 1.920 AT 0.480 BC 37E000 376.000 260.000 260.000 5.040 AL 4.650 AL 4.260 AL 4.030 AL 3.880 AL 1 .660BC 1.800BC HCMS HCIV1S MPS HCMS HCMS NM HCIVIS NM FSA FSA 2710 2711 2711 2712 2713 2713 2714 2716 2719M 271912 HP HP NSC HP HP NSC HP NSC NSC NSC 35.840 A 37.950 A 0.170 N 37.950 A 37.950 A 0.170 N 37.950 A 0.170 N 4.380 I 2.820 I 33.090 Z 35.030 Z 0.130 BC 35.030 Z 35.030 Z 0.110 BC 35.030 Z 0.110 BC 3.370 AL 2.170 AL 30.720 AE 28.670 AL 32530 AE 30.360 AL 0.100 BD 32.53

CE = Vit Vit Input Low Voltage -0.1 0.8 v Vin Input High Voltage 2.0 Voc + 1 Vv VoL Output Low Voitage 0.45 Vv lo. = 2.1 mA Vou Output High Voltage 2.4 Vv lon = 400 nA A.C. CHARACTERISTICS oc < Ta < 70C Versions Voc +5% 2732A-2 2732A Test Voc 10% 2732A-20 2732A-25 Units Conditions Symbol Parameter Min | Max | Min | Max tacc Address to Output Delay 200 250 ns CE = OF = Vi tcE CE to Output Delay 200 250 ns OE = ViL toe OE/Vpp to Output Delay 70 100 ns CE = Vit tori) OE/Vpp High to Output Float 60 60 ns CE = Vit ton(4) Output Hold from Addresses, ns CE = OE = ViL CE or OE/Vpp, Whichever Occurred First NOTES: 1. Voc must be applied simultaneously or before OE/Vpp and removed simultaneously or after GE/Vpp. 2. The maximum current value is with outputs Og to O7 unloaded. 3. Typical values are for Ta = 25C and nominal supply voltages. 4. This parameter is only sampled and is not 100% tested. Output Float is defined as the point where data is no longer drivensee timing diagram.intel 2732A CAPACITANCE (2)

PRODUCTS PRELIMINARY HD63P05Y 1, HD63PA05Y 1, HD63PBO5Y 1 {OC-64SP) = PIN ARRANGEMENT Type No. Bus Timing Applied EPROM HD63P05Y 1 1 MHz HN482732A-30, HN482764-3, HN27C64-30 HD63PA05Y1] 1.5 MHz | HN482732A-30, HN482764-3, HN27C64-30 HD63PB0SY1| 2 MHz HN482732A-25, HN482764, HN27C64-25 (Note) EPROM is not attached to the MCU. @ PROGRAM DEVELOPMENT SUPPORT TOOLS @ Cross assembler software for use with IBM PCs and compatibles @ Incircuit emulator for use with |BM PCs and compatibles {Top View} @ HITACHI Hitachi America, Ltd. e Hitachi Plaza * 2000 Sierra Point Pkwy. Brisbane, CA 94005-1819 (415) 589-8300 599HD63P05Y1, HD63PA05Y1, HD63PBO5Y1 = BLOCK DIAGRAM | iP XTAL EXTAL AAWAESNUM iNT STeY i i Miscella- Pri Timer/ J Oscillator = TIMER aot escaler F Counter neous 7 Register Timer contra Accumulator hg +__ ok A Ay -e} ge cPU 0, Port A Awe te ES Index Control . OwinT, Ape re [Os ij = Register x 0 &h od, ter 4 82 | 22 KO p] 2 BE a: Porro Terminals a,, a] ox as Condition Code 5 SR 9, _~sInour Ag _o = R