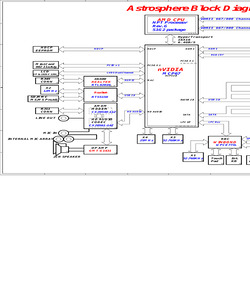

P4 P1 R1 M1 26MIL 1 U2A H_A#3 H_A#4 H_A#5 H_A#6 H_A#7 H_A#8 H_A#9 H_A#10 H_A#11 H_A#12 H_A#13 H_A#14 H_A#15 H_A#16 2 2 5 CPU SOCKET_478P FOX_PZ4782A-274M-01 B B 1 +1_05VRUN R42 2 1 +3VRUN 6 R43 2.2K_J 0402 PROCHOT# Q1A 2 Q1B G1 S1 1 2 D1 A0205 3 68_J 0402 2N7002SPT D2 5 G2 S2 4 41,53,71 OVT_EC# OVT_EC# 2N7002SPT A A HAI PRECISION IND. CO., LTD. FOXCONN HON CPBG - R&D Division Title Penryn (HOST BUS) 1/3 Size A3 Date: 5 4 3 2 Document Number Rev M780(MBX-194) Friday, June 13, 2008 0.1 Sheet 1 4 of 79 5 4 3 2 1 D D U2B C 7 7 7 H_D#16 H_D#17 H_D#18 H_D#19 H_D#20 H_D#21 H_D#22 H_D#23 H_D#24 H_D#25 H_D#26 H_D#27 H_D#28 H_D#29 H_D#30 H_D#31 2 Layout Note: Zo=55 ohm, 0.5" max for GTLREF. R44 2K_F 0402 1 R48 B H_DSTBN#1 H_DSTBP#1 H_DINV#1 1 7 7 7 H_GTLREF 2 Place close to CPU 1K_F 0402 Route the TEST3 and TEST5 signals through a ground referenced Zo = 55-ohm trace that ends in a via that is near a GND via and is accessible through an oscilloscope connection. TEST4 and TEST6 and TEST7 pins ca

2 SYS_PRS# 51 1 2SYS_PRS#_1 2 PR21 330_J 0402 1 PCN2 GND IINP CCV CCI CCS MAX1909_REF 2 S 1 2 PR43 100K_J 0402 1 2 DC_IN_MOS MAIN_DC_SW_OFF# MMVZ5235BPT PD10 1 6 3 2 1 6 2 ALW_ON 27,46,51 BAS316PT A D1 D2 DC_IN_G1 2 G1 1 5 S1 2 2 1 PD11 BAT54WAPT G2 PQ17A 2N7002SPT S2 4 1 PR46 10K_F 0402 3 1 AC_OFF_3# 1 PD9 PQ17B 2N7002SPT FOXCONN PR168 47K_J 0402 Title 2 Size A3 MAIN_DC_SW_OFF# Date: 5 B PR34 20K_F 0402 MAX1909_CSSP MAX1909_PDS 2 2 PR48 200K_J 0402 PQ12B PUMB2 PR50 0_J 0402 51 PC40 1U_25V_M_B 0603 2 2 1 2 1 4 E 2 23.2K_F 0402 1 G 4 1 3 C PQ5B MUN5213DW1T1G 6 1 PQ5A MUN5213DW1T1G 3 2 PQ4 2PC4617Q 2 1 PC42 0603 0.22U_16V_K_B 5 B 1 PR32 PRG18BB330MB1RB 1 2 PD8 MMPZ5246BPT 2 1 2 4 3 2 1 1 1 2 3 1 2 B E 1 C 2 PR44 200K_J 0402 B PR11 1K_F 0402 ENCHG#_1 C 2 E REF PQ11 IRLML5103PbF PR36 3 1 E PR10 10K_F 0402 B 3 AC_OFF_3# 51 C 1 2 ENCHG# PQ13 2N7002 1 PU1 AME431BBJETB25Z A 27 MAX1909_CLS C PQ12A PUMB2 D 20K_F 0402 E B 5 PR5 120K_J 0402 S 2 PR4 10K_J 0402 2 PR41 10K_J 0402 G 2 1 PD2 MMPZ5250

2N7002SPT SURFACE MOUNT Dual N-Channel Enhancement MOS FET VOLTAGE 60 Volts CURRENT 0.250 Ampere APPLICATION * Servo motor control. * Power MOSFET gate drivers. * Other switching applications. FEATURE SC-88/SOT-363 * Small surface mounting type. (SC-88/SOT-363) * High density cell design for low R DS(ON). * Suitable for high packing density. (1)(S1) * Rugged and reliable. * High saturation current capability. * Voltage controlled small signal switch. 1.2~1.4 (D1)(6) 0.65 (G1) (G2) (D2) CONSTRUCTION 0.15~0.35 (3) 2.0~2.2 0.65 (S2)(4) 1.15~1.35 * Dual N-Channel Enhancement MARKING * 702S 0.8~1.1 0.08~0.15 0~0.1 0.1 Min. CIRCUIT (6) D1 (1)S1 G2 S2(4) 2.15~2.45 Dimensions in millimeters D2(3) G1 Absolute Maximum Ratings SC-88/SOT-363 TA = 25C unless otherwise noted 2N7002SPT Symbol Parameter VDSS Drain-Source Voltage 60 V VDGR Drain-Gate Voltage (RGS < 1 M) 60 V VGSS Gate-Source Voltage - Continuous 20 - Non Repetitive (tp < 50s) ID Maximum Drain Current - Continuous - Pulsed PD Maximum

shift Q15 13 NB_DDCDATA 2 5V_CRT_S0 5V_S0 D5 DDC_CLK_CON 4 3 5 2 6 DDC_DATA_CON 1 NB_DDCCLK 2 CRT_R DY 13 NB_HSYNC VSYNC_5 1OE 1A 2Y GND VCC 2OE 1Y 2A 8 7 6 5 VSYNC_5 HSYNC_5 SSHCT2G126DP-GP 2 1 13 3 4 5V @ ext. CRT side 1 BAV99PT-GP-U D4 RN23 NB_VSYNC 13 2N7002SPT 3 U11 1 2 3 4 2 JVGA_VS JVGA_HS 2 SRN33J-5-GP-U CRT_G 3 DY 1 BAV99PT-GP-U D2 2 CRT_B 3 DY 1 BAV99PT-GP-U 1 1 Wistron Corporation 21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C. Title CRT Connector Size A3 Document Number Rev DS2-AMD Date: Monday, September 24, 2007 A B C D 1 Sheet E 17 of 44 B C D E 1 A R110 8K2R2J-3-GP 1 1 PCIE_CALRP 2 562R2F-GP 2 2K05R2F-GP PCIE_CALRN E29 E28 PCIE_CALRP PCIE_CALRN R326 1 2 0R0402-PAD E27 PCIE_CALI U29 PCIE_PVDD U28 PCIE_PVSS F27 F28 F29 G26 G27 G28 G29 J27 J29 L25 L26 L29 N29 PCIE_VDDR PCIE_VDDR PCIE_VDDR PCIE_VDDR PCIE_VDDR PCIE_VDDR PCIE_VDDR PCIE_VDDR PCIE_VDDR PCIE_VDDR PCIE_VDDR PCIE_VDDR PCIE_VDDR PCIE_CALI 1 2 C554 SC1U10V3KX-3GP C273 SC1U10V2ZY 1D2V_S

38 U38 T38 J38 F38 C38 BF37 BB37 AW37 AT37 AN37 AJ37 H37 C37 BG36 BD36 AK15 AU36 Place R105 close to MCH within 500 mils. D C B CANTIGA-GM-GP-U-NF NCTF PIN +3.3V_RUN RN2 +3.3V_RUN 3 4 2 1 SRN2K2J-1-GP U4 GMCH_DDCDATA 45 DDC_CLK_CON DDC_CLK_CON 4 3 5 2 6 1 2N7002SPT DDC_DATA_CON DDC_DATA_CON 45 GMCH_DDCCLK 5V @ ext. CRT side A Wistron Corporation CANTIGA-GM-GP-U-NF 21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C. CANTIGA-GM-GP-U-NF Title Cantiga-GND/LVDS/VGA(6/6) Size Document Number Custom Date: Friday, June 27, 2008 Sheet Rev SB Roberts 13 of 57 5 4 3 2 1 DM2 1 TC8 ST220U2D5VBM-LGP DY 2 1 C106 SCD1U16V2KX-3GP 2 1 C100 SCD1U16V2KX-3GP 2 1 C109 SCD1U16V2KX-3GP 2 1 C93 SCD1U16V2KX-3GP DY 2 1 2 2 DY C116 SC2D2U10V3KX-1GP 1 C138 SC2D2U10V3KX-1GP 1 DY 2 1 2 C122 SC2D2U10V3KX-1GP 1 2 C132 SC2D2U10V3KX-1GP C C160 SC2D2U10V3KX-1GP Layout Note: Place near DM1 +1.8V_SUS Layout Note: Place one cap close to every 2 pullup resistors terminated to +0.9V_DDR_VTT. 1 2 C420

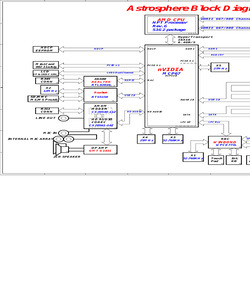

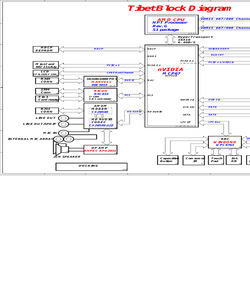

V2KX-2GP SENSE1 CPU_THERMDC 5 17,30,35,37,38,41 +3VS 4 3 74LVC1G08GW-1-GP +3VS +3VS RN36 SRN2K7J-3-GP 1 1 2 DY R193 10KR2J-3-GP EC_RST# D . . . . 30 . 2 Q6 G S PV 0326 U25 SMBD_G792 G792_ALERT# 2N7002E-1-GP 30 KBC_SCL1 3 4 2 5 1 6 KBC_SDA1 30 SMBC_G792 DY 2N7002SPT 2 R577 1 0R0402-PAD 2 R578 1 0R0402-PAD Wistron Corporation 21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C. Title Thermal/Fan Controllor Size Custom Document Number Date: Monday, June 09, 2008 Rev Astrosphere Sheet 23 SA of 44 SATA HD Connector PV 0407 ODD Connector HDD1 23 NP1 1 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 NP2 24 USB20_P4 1 USB20_N6 TP28-75-GP TP33 1 USB20_P6 TP28-75-GP TP36 1 TP28-75-GP TP34 1 TP28-75-GP TP31 1 1 SI 0107 1 +3VL 2 +5VS NUMLK_LED NUMLK_LED 3 DY 1 USB PORT 1 D38 1 TP28-75-GP TP169 R534 DY 1115 DB Close to USB1 2 1 S1 S4 S7 P5 P6 8 9 ODD_MD TP161 BAV99W-1-GP +5V_USB +5V_USB2 DY F3 1 100 mil 2 FUSE-2A8V-3GP C568 2 +5V_USB1 SI 0102 EC77 1 1 TP28-75-GP TP35 NP1 NP2 GN

V2JN-3GP NC#5 NC#2 VGA_TV_LUMA VGA_TV_CRMA VGA_TV_COMP 2 SC8P250V2CC-GP 1 2 L3 IND-D56UH-16-GP LUMA CRMA COMP TV_COMP 16 2 C12 11 VGA_TV_LUMA 1 TV_COMP MINDIN7-16-GP-U 1 6 DDC_DATA_CON 2 TV1 C7 SC82P50V2JN-3GP 2 CHBD2004SPT-GP 1 1 2 L2 IND-D56UH-16-GP 3 5 2N7002SPT Thr org part is 68.2703N.10B C3 SC82P50V2JN-3GP 4 3D3V_S0 TV_CRMA 16 2 SC8P250V2CC-GP 2 1 1 2 C4 SC82P50V2JN-3GP JVGA_VS 2 0R0402-PAD 1 2 C9 11 VGA_TV_COMP 1 L9 1 C1 SC82P50V2JN-3GP 2 L1 IND-D56UH-16-GP 2 1 11 VGA_TV_CRMA JVGA_VS_L 16 DDC_CLK_CON R3 150R2F-1-GP 1 JVGA_HS 2 0R0402-PAD R1 150R2F-1-GP 2 1 C5 1 L8 R2 150R2F-1-GP 2 1 Layout Note: Place this 2 resistors close to the TV-out connector JVGA_HS_L U6 11 DDC_VGA_5V_DAT DY 2 TV OUT CONN CRT_B 2 4 3 2 1 2 2 VSYNC_5 SRN33J-5-GP-U A C13 DY Do Not Stuff 2 DY R12 150R2F-1-GP 1 1 DY Do Not Stuff 2 C15 3 1 1 1 VIDEO-15-57-GP-U1 4 14 14 Do Not Stuff 3 7 JVGA_HS 15 VGA_RED VGA_GREEN VGA_BLUE R7 150R2F-1-GP 2 1 DDC_DATA_CON DY 6 7 1 14 11,16 VGA_VSYNC 13 1 5V_CRT_S0 2 JVGA_HS 2 DDC_DATA_CON

27 7 8 MAX1909_DLOV 6 DAT_SMB 5 CLK_SMB 4 BATT_PRS# 1 2BATT_PRS#_1 3 PR20 330_J 0402 SYS_PRS# 51 1 2SYS_PRS#_1 2 PR21 330_J 0402 1 27 PCN2 GND IINP CCV CCI CCS MAX1909_REF 2 2 PVT 1 2 3 6 2 ALW_ON 27,46,51 BAS316PT A D1 D2 DC_IN_G1 1 G1 5 2 1 S1 G2 PQ17A 2N7002SPT S2 4 2 PD11 BAT54WAPT PQ17B 2N7002SPT FOXCONN PR168 47K_J 0402 Title 2 Size A3 MAIN_DC_SW_OFF# 4 1 PD10 1 Date: 5 2 DC_IN_MOS MAIN_DC_SW_OFF# MMVZ5235BPT 2 PR46 10K_F 0402 1 6 1 1 PD9 3 1 AC_OFF_3# B PR43 100K_J 0402 MAX1909_PDS 2 2 PR48 200K_J 0402 PQ12B PUMB2 PR50 0_J 0402 51 DVT PR34 20K_F 0402 MAX1909_CSSP 2 1 2 1 4 E PC40 1U_25V_M_B 0603 PRG18BB330MB1RB 2 3 C 2 23.2K_F 0402 1 G 4 1 PR44 200K_J 0402 PQ5B MUN5213DW1T1G 6 1 PQ5A MUN5213DW1T1G 3 2 PQ4 2PC4617Q 2 1 PC42 0603 0.22U_16V_K_B 5 B 1 PR32 DVT 1 2 PD8 MMPZ5246BPT 2 1 2 4 3 2 1 1 1 2 3 1 2 B 1 C E 2 ENCHG#_1 B PR11 1K_F 0402 REF PD7 PACDN042Y3R DVT C C 2 E MAX1909_CLS PQ11 IRLML5103PbF PR36 3 1 E PR10 10K_F 0402 B 3 AC_OFF_3# 51 C 1 2 ENCHG# PQ13 2N7002 1 PU1 AME4

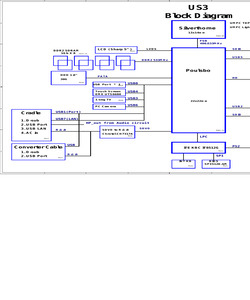

W +3.3V_RUN PSDAT1 TPDATA PSCLK1 TPCLK ICH9M SMBCLK SMB_CLK SMBDATA SMB_DATA TPDATA TPCLK TPCLK 45 SRN2K2J-1-GP DIMM 1 ICH_SMBCLK ICH_SMBDATA SCL SDA SRN4K7J-8-GP 16 SMBus Address:A0 20 TPDATA +3.3V_RTC_LDO +3.3V_RUN SRN2K2J-1-GP SCL1 BAT_SCL SDA1 BAT_SDA 2N7002SPT DIMM 2 ICH_SMBCLK ICH_SMBDATA SDA Battery Conn. SRN100J-3-GP PBAT_SMBCLK1 CLK_SMB PBAT_SMBDAT1 DAT_SMB KBC SCL 17 SMBus Address:A4 2 SMB_CLK SMB_DATA SMB_CLK SMB_DATA 50 ICH_SMBCLK ICH_SMBDATA MAX8731 WPC773L SCL Clock Generator SMBus address:12 09 +3.3V_RTC_LDO SMBus address:D2 SMB_CLK SMB_DATA +3.3V_RUN Minicard WLAN SRN4K7J-8-GP SMB_CLK SMB_DATA 2 32 +3.3V_RUN SCLK SDATA SMBus address:16 31 SDA Express Card 1 TouchPad Conn. GPIO73/SCL2 KBC_SCL1 GPIO74/SDA2 KBC_SDA1 43 SRN4K7J-8-GP Thermal THERM_SCL SCL THERM_SDA SDA SMBus address:7A 28 2N7002DW-1-GP 26 +3.3V_RUN 3 3 SRN2K2J-1-GP DDC1CLK LDDC_CLK DDC1DATA LDDC_DATA LCD Conn. 41 +3.3V_DELAY VGA +5V_CRT_RUN SRN2K2J-1-GP DDC2CLK M92CRT_DDCCLK M92CRT_DDCDATA DDC2DATA 4 +3.3V_DELAY SRN2K2

402 SYS_PRS# 51 1 2SYS_PRS#_1 2 PR21 330_J 0402 1 PCN2 GND IINP CCV CCI CCS MAX1909_REF 2 1 2 PR43 100K_J 0402 1 2 DC_IN_MOS MAIN_DC_SW_OFF# MMVZ5235BPT PD10 1 6 3 2 1 6 2 ALW_ON 27,46,51 BAS316PT A D1 D2 DC_IN_G1 2 G1 1 5 S1 2 2 1 PD11 BAT54WAPT G2 PQ17A 2N7002SPT S2 4 1 PR46 10K_F 0402 3 1 AC_OFF_3# 1 PD9 PQ17B 2N7002SPT FOXCONN PR168 47K_J 0402 Title 2 Size A3 MAIN_DC_SW_OFF# Date: 5 B PR34 20K_F 0402 MAX1909_CSSP MAX1909_PDS 2 2 PR48 200K_J 0402 PQ12B PUMB2 PR50 0_J 0402 51 PC40 1U_25V_M_B 0603 2 2 1 2 1 4 E 2 23.2K_F 0402 1 G 4 1 3 C PQ5B MUN5213DW1T1G 6 1 PQ5A MUN5213DW1T1G 3 2 PQ4 2PC4617Q 2 1 PC42 0603 0.22U_16V_K_B DVT 5 B 1 PR32 PRG18BB330MB1RB 1 2 PD8 MMPZ5246BPT 2 1 2 4 3 2 1 1 1 2 3 1 2 B E 1 C 2 PR44 200K_J 0402 B PR11 1K_F 0402 ENCHG#_1 C 2 E REF PQ11 IRLML5103PbF PR36 3 1 E PR10 10K_F 0402 B 3 AC_OFF_3# 51 C 1 2 ENCHG# PQ13 2N7002 1 PU1 AME431BBJETB25Z A 27 MAX1909_CLS C PQ12A PUMB2 D 20K_F 0402 E B 5 PR5 120K_J 0402 S 2 PR4 10K_J 0402 2 PR41 10K_J 0402 G 2 1 PD2 MMPZ

1-GP DY 4 3 2 0R0603-PAD HDMI_TXD#1 SB:06/23 Add R444,R445(63.R0034.1DL) DY R73 10KR2J-3-GP 2 R288 1 23 HDMI_TXD#1 E 1 2 A 4 4 L21 ACM2012H-900-GP DY DY HDMI_SCLK 23 HDMI_TXD1 HDMI_TXD1 R292 HDMI_TXD1_C 1 2 23 HDMI_TXD0 3 2 3 2 HDMI_SDATA_C R285 6 2 5 3 4 2N7002SPT HDMI_TXD0 0R0603-PAD 1 1 2 HDMI_SDATA connect to 5V_S0 directly. R445 1 1 R299 4 1 HDMI_TXD#1_C HDMI_TXD1_C +5V_POWER 9 7 TMDS_DATA0TMDS_DATA0+ 6 4 TMDS_DATA1TMDS_DATA1+ SB:06/22 Change R66,R67 from 63.R0034.1DL to ZZ.R0402.ZZZ 18 SDA 16 HDMI_SDATA_C SCL 15 HDMI_SCLK_C CEC 13 HDMI_CEC R67 1 2 1 2 R66 TP91 TPAD28 HDMI_TXD#2_C HDMI_TXD2_C 3 1 TMDS_DATA2TMDS_DATA2+ DY DY 14 TP90 TPAD28 12 10 RESERVED#14 HDMI_CNC HDMI_TX#C_C HDMI_TXC_C TMDS_CLOCKTMDS_CLOCK+ HOT_PLUG_DETECT 19 HDMI_DP_C2 1 8 5 2 11 DDC/CEC_GROUNG GND TMDS_DATA0_SHIELD GND TMDS_DATA1_SHIELD GND TMDS_DATA2_SHIELD GND TMDS_CLOCK_SHIELD 17 20 21 22 23 2 L20 ACM2012H-900-GP 23 HDMI_TXC HDMI_TXC HDMI_TXC_C 1 R277 0R0603-PAD 2 0R0603-PAD SB:06/23 Add R444,R445(63.R0034.1DL) RN17 S

XD#0 RN23 SRN2K2J-1-GP DY 4 3 1 R345 2 0R0603-PAD 2 -1 HDMI_TXD#0 E 3D3V_S0 1 HDMI I/F & CONNECTOR 49 HDMI_TXD#1 D 1 2 A DY HDMI_TXD#0_C 1 1 L30 ACM2012H-900-GP L29 ACM2012H-900-GP DY DY HDMI_SDATA_C 1 6 2 5 3 4 HDMI_SCLK_C 5V_S0 HDMI_SDATA D12 DY 3 2 3 2 2N7002SPT 1 5V_S0 +5V_HDMI 1 R336 2 0R0603-PAD HDMI_TX#C_C HDMI_TXD#0_C HDMI_TXD0_C 9 7 TMDS_DATA0TMDS_DATA0+ HDMI_TXD#1_C HDMI_TXD1_C 6 4 TMDS_DATA1TMDS_DATA1+ L28 ACM2012H-900-GP HDMI_TXD#2_C HDMI_TXD2_C 3 1 TMDS_DATA2TMDS_DATA2+ DY DY HDMI_TX#C_C HDMI_TXC_C 12 10 TMDS_CLOCKTMDS_CLOCK+ 8 5 2 11 TMDS_DATA0_SHIELD TMDS_DATA1_SHIELD TMDS_DATA2_SHIELD TMDS_CLOCK_SHIELD 2 L31 ACM2012H-900-GP 3 2 HDMI_TXD2 HDMI1 -1 HDMI_TX#C 1 49 HDMI_TX#C 4 HDMI_TXD#2_C 1 HDMI_TXD#2 2 49 HDMI_TXD2 -1 4 1 R350 2 0R0603-PAD 49 HDMI_TXD#2 SC HDMI CONN 1 R344 2 0R0603-PAD HDMI_TXD2_C 49 HDMI_TXC HDMI_TXC 1 R352 2 0R0603-PAD HDMI_TXC_C 1 R337 2 0R0603-PAD -1 +5V_POWER 18 SDA 16 SCL 15 CEC 13 3 2 BAS16-1-GP RN20 SRN1KJ-7-GP RESERVED#14 14 HOT_PLUG_DETECT 19 DDC/CEC_GROUN

38 U38 T38 J38 F38 C38 BF37 BB37 AW37 AT37 AN37 AJ37 H37 C37 BG36 BD36 AK15 AU36 Place R105 close to MCH within 500 mils. D C B CANTIGA-GM-GP-U-NF NCTF PIN +3.3V_RUN RN2 +3.3V_RUN 3 4 2 1 SRN2K2J-1-GP U4 GMCH_DDCDATA 45 DDC_CLK_CON DDC_CLK_CON 4 3 5 2 6 1 2N7002SPT DDC_DATA_CON DDC_DATA_CON 45 GMCH_DDCCLK 5V @ ext. CRT side A Wistron Corporation CANTIGA-GM-GP-U-NF 21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C. CANTIGA-GM-GP-U-NF Title Cantiga-GND/LVDS/VGA(6/6) Size Document Number Custom Date: Thursday, October 02, 2008 Sheet Rev A00 Roberts 13 of 58 5 4 3 2 1 DM2 1 TC8 ST220U2D5VBM-LGP DY 2 1 C106 SCD1U16V2KX-3GP 2 1 C100 SCD1U16V2KX-3GP 2 1 C109 SCD1U16V2KX-3GP 2 1 C93 SCD1U16V2KX-3GP DY 2 1 2 2 DY C116 SC2D2U10V3KX-1GP 1 C138 SC2D2U10V3KX-1GP 1 DY 2 1 2 C122 SC2D2U10V3KX-1GP 1 2 C132 SC2D2U10V3KX-1GP C C160 SC2D2U10V3KX-1GP Layout Note: Place near DM1 +1.8V_SUS Layout Note: Place one cap close to every 2 pullup resistors terminated to +0.9V_DDR_VTT. 1

V2KX-2GP SENSE1 CPU_THERMDC 5 17,30,35,37,38,41 +3VS 4 3 74LVC1G08GW-1-GP +3VS +3VS RN36 SRN2K7J-3-GP 1 1 2 DY R193 10KR2J-3-GP EC_RST# D . . . . 30 . 2 Q6 G S PV 0326 U25 SMBD_G792 G792_ALERT# 2N7002E-1-GP 30 KBC_SCL1 3 4 2 5 1 6 KBC_SDA1 30 SMBC_G792 DY 2N7002SPT 2 R577 1 0R0402-PAD 2 R578 1 0R0402-PAD Wistron Corporation 21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C. Title Thermal/Fan Controllor Size Custom Document Number Date: Tuesday, April 29, 2008 Rev Astrosphere Sheet 23 SA of 44 SATA HD Connector PV 0407 ODD Connector HDD1 23 NP1 1 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 NP2 24 USB20_P4 1 USB20_N6 TP28-75-GP TP33 1 USB20_P6 TP28-75-GP TP36 1 TP28-75-GP TP34 1 TP28-75-GP TP31 1 1 SI 0107 1 +3VL 2 +5VS NUMLK_LED NUMLK_LED 3 DY 1 USB PORT 1 D38 1 TP28-75-GP TP169 R534 DY 1115 DB Close to USB1 2 1 S1 S4 S7 P5 P6 8 9 ODD_MD TP161 BAV99W-1-GP +5V_USB +5V_USB2 DY F3 1 100 mil 2 FUSE-2A8V-3GP C568 2 +5V_USB1 SI 0102 EC77 1 1 TP28-75-GP TP35 NP1 NP2

LCDKB_SW# B D16 CH501S KBSW# 19,21 B Fix KBSW# will driving down when TP power off LCD Blacklight control level shift VCC5 VCC5 R122 10K VCC5 R123 10K R121 10K Q24 8 LVDS_BKLTCTL LCD_BKCTL 1 2 3 S1 D1 G1 G2 D2 S2 R225 6 5 4 VCC5 8 LVDS_BKLEN 100K LCD_BKEN 2N7002SPT R125 10K Q23 1 2 3 S1 D1 G1 G2 D2 S2 6 5 4 2N7002SPT A A QUANTA COMPUTER HW Engineer : Title Size : Touch Screen/LCD Document Number : Rev : A X Date : 5 4 3 2 Thursday, May 01, 2008 Sheet 1 15 of 26 5 4 3 2 1 VCC2.5 D DVDD L16 VCC2.5 C SDVO_CTRLDAT SDVO_CTRLCLK R230 R231 3.5K 3.5K 2 3 17 17 17 CRT_R CRT_G CRT_B 20 24 28 R G B 17 17 VGAHSYNC VGAVSYNC 34 36 HSYNC VSYNC SC_EEPROM SD_EEPROM T97 T102 C271 9,19,21 EC_PLTRST# 56P VCC2.5 DDCDATA DDCCLK AS SDVO_CTRLDAT SDVO_CTRLCLK 8 SDVO_CTRLDAT 8 SDVO_CTRLCLK 8 SDVO_R+ 8 SDVO_R8 SDVO_G+ 8 SDVO_G8 SDVO_B+ 8 SDVO_B8 SDVO_CLK+ 8 SDVO_CLK- R203 10K AS R204 *10K C289 C298 C299 C300 C301 C302 C310 C311 0.1U 0.1U 0.1U 0.1U 0.1U 0.1U 0.1U 0.1U SDVO_R+_R SDVO_R-_R SDVO_G+_R SDVO_G-_R SDV