Hz 2 C6 0.1U_0402_16V4Z~D FSA 2 1 C5 0.1U_0402_16V4Z~D FSB 2 1 2 C10 0.1U_0402_16V4Z~D FSC CLKSEL2 CLKSEL1 CLKSEL0 2 1 @ 2 +CK_VDD_REF C13 0.047U_0402_16V7K~D 1 1 2 @R9 @R9 0_0402_5%~D 1 C9 0.1U_0402_16V4Z~D +CK_VDD_48 CLK_SCLK C12 0.047U_0402_16V4Z~D Q1B 2N7002DW-T/R7_SOT363-6~D 4 C11 4.7U_0603_6.3V4Z~D 3 C8 10U_0805_10V4Z~D 1 +3.3V_M <27,38,48> CKG_SMBCLK 2 MINI2CLK_REQ# 1 2 @ L2 @L2 BLM21PG600SN1D_0805~D Q1A 2N7002DW-T/R7_SOT363-6~D 1 C4 0.1U_0402_16V4Z~D +CK_VDD_MAIN2 2 C3 0.1U_0402_16V4Z~D CLK_SDATA 1 C2 10U_0805_10V4Z~D D 2 1 +CK_VDD_MAIN 1 2 L1 BK2125HS601-T 0805~D R851 0_0805_5%~D 1 R2 2.2K_0402_5%~D 6 <27,38,48> CKG_SMBDAT R1 2.2K_0402_5%~D 1 2 @ R3 @R3 0_0402_5%~D 1 C1 0.1U_0402_16V4Z~D +3.3V_M 2 +CK_VDD_MAIN 1 R49 1 R52 SATA_CLKREQ#_R 1 R53 DOT96_SSC 1 R523 DOT96_SSC# 1 R670 CLK_MCH_3GPLL <10> CLK_MCH_3GPLL# <10> CLK_3GPLLREQ# <10> CLK_PCIE_SATA <23> CLK_PCIE_SATA# <23> SATA_CLKREQ# <24> A DREF_SSCLK <10> DREF_SSCLK# <10> DELL CONFIDENTIAL/PROPRIETARY SLG8LP554VTR_QFN72_10

0402_16V4Z~D FSC CLKSEL2 2 2 C13 0.047U_0402_16V7K~D 2 1 @ 1 +CK_VDD_REF C12 0.047U_0402_16V4Z~D 1 C11 4.7U_0603_6.3V4Z~D 1 2 @R9 0_0402_5%~D 1 C9 0.1U_0402_16V4Z~D +CK_VDD_48 C3 0.1U_0402_16V4Z~D CLK_SCLK 2 C8 10U_0805_10V4Z~D 3 <27,38,48> CKG_SMBCLK Q1B 2N7002DW-T/R7_SOT363-6~D 4 1 MINI2CLK_REQ# 1 2 @ L2 BLM21PG600SN1D_0805~D +3.3V_M D +CK_VDD_MAIN2 2 C2 10U_0805_10V4Z~D CLK_SDATA Q1A 2N7002DW-T/R7_SOT363-6~D 1 R851 0_0805_5%~D 1 2 1 +CK_VDD_MAIN 1 2 L1 BLM21AG601SN1D_0805~D C1 0.1U_0402_16V4Z~D 6 <27,38,48> CKG_SMBDAT R2 2.2K_0402_5%~D 1 2 @ R3 0_0402_5%~D R1 2.2K_0402_5%~D 1 +3.3V_M 1 2 +CK_VDD_MAIN 1 R49 1 R52 SATA_CLKREQ#_R 1 R53 CLK_MCH_3GPLL <10> CLK_3GPLLREQ# <10> CLK_PCIE_SATA <23> SATA_CLKREQ# <24> A DELL CONFIDENTIAL/PROPRIETARY SLG8LP554VTR_QFN72_10X10~D Compal Electronics, Inc. PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT BE TRANSFER

CPU 1.05V SHIFTER 53398-0476 10K TP_SMC_SMB_0_CLK F-ST-SM 5 10K 1 2 R5916 SMC_LID 58 PP3V3_S3 83 59 53 6 1 I2C_ALS_SDA I2C_ALS_SCL 59 59 2 59 7 SMC_EXCARD_PWR_EN SMC_PB7 58 SMC_FAN_3_TACH 58 SMC_FAN_3_CTL CPU_PROCHOT_L 58 3 59 6 4 Q5901 D TPM RESET PULLUP 2N7002DW-X-F 6 58 SMC_PROCHOT 2 G 67 SOT-363 S 67 58 PP3V3_TPM_3VSB R58271 SMC_TPM_RESET_L TP_SMC_EXCARD_PWR_EN MAKE_BASE=TRUE TP_SMC_PB7 MAKE_BASE=TRUE TP_SMC_FAN_3_TACH MAKE_BASE=TRUE TP_SMC_FAN_3_CTL MAKE_BASE=TRUE FUNC_TEST=TRUE PULLDOWNS FOR SYSTEM STATE PINS FUNC_TEST=TRUE FUNC_TEST=TRUE 10K POWER BUTTON HEADER (REF DES PRESERVED FOR PLACEMENT PURPOSE) WIRE-OR DIMM OVERTEMP TO SMC 29 28 21 14 7 POWER_BUTTON_L SMC PULL-UPS PM_EXTTS_L<0> 58 Q5901 D 59 58 6 GPUVCORE_IOUT SMC_GPU_ISENSE 85 MAKE_BASE=TRUE 59 58 2N7002DW-X-F 58 1 SMC_THRMTRIP 5 G 58 SOT-363 S 58 58 2 =PP3V3_S5_SMC 5% 1/16W MF-LF 402 SENSE GPU REGULATOR OUTPUT CURRENT 3 59 58 IO 59 58 IO 14 58 MAKE_BASE=TRUE M-ST-SM 3 5 DIMM_OVERTEMP_L PM_THRMTRIP_L 53398-0276 R5917

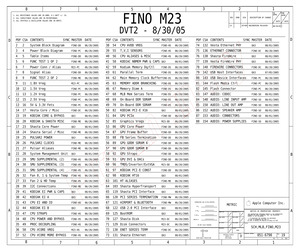

V 4 3 3 5% 1/16W MF-LF 402 RDSON=0.04 OHM @ VGS=2.5 V TSOP-LF Q1503_G R1509 2 100K 1 Q1506_G C1582 0.01UF 5% 1/16W MF-LF 402 NOSTUFF OPTION TO DELAY 2.5V PWRON TO COME UP WITH 3.3V PWRON 16 4 TURN_ON_PP3V3_PWRON_L 1 NOSTUFF R1512 1 0 3 2 PWRON_L 1 0 1 G 6 2N7002DW-X-FD SOT23-LF S 3 Q1504 2N7002 Q1505_G R1513 16 13 12 11 Q1505 D 5% 1/16W MF-LF 402 2 20% 16V CERM 402 5 2 G Q1504 D 2N7002DW-X-F SOT-363 SOT-363 S S G 2 SYS_SLEEP 11 12 13 16 26 30 54 2 4 5% 1/16W MF-LF 402 1 2.5V Vreg A SYNC_MASTER=FINO-M23 SYNC_DATE=08/26/2005 NOTICE OF PROPRIETARY PROPERTY THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR AGREES TO THE FOLLOWING I TO MAINTAIN THE DOCUMENT IN CONFIDENCE II NOT TO REPRODUCE OR COPY IT III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART SIZE APPLE COMPUTER INC. DRAWING NUMBER SCALE SHT NONE 8 7 6 5 4 3 2 REV. 051-6863 D 15 1 OF F 154 A 8 6 7 2 3 4 5 1 D D PP5V_ALL PP12V_ALL 1 R16021 C1600 0.01UF 20% 16V 2 CERM 402 3.6K 5% 1/16W MF

7 100K 1% 1/16W MF-LF 2 402 R1209 1% 1/16W MF-LF 470K 1 402 R1202 97.6K C1200 1 R1204 14 1V20_REF 2 4 AC_DET_DIV 3 10K 1% 1/16W MF-LF 402 1 25 18 13 5 R12052 1M SYS_ACIN_L D SOT23-LF S R1227 1 4.7M 2 5% 1/16W MF-LF 402 R1226 127K 1% 1/16W MF-LF 2 402 13 C 2N7002DW-X-F 2 5 5% 1/16W MF-LF 402 1% 1/16W MF-LF 402 1 Q1208 A29_DET_L G 2 1 1% 1/16W MF-LF 2 402 4 1 V5 402K SOT-363 S 3 R1206 1 57.6K G 3 11 A29_DET_REF R1223 2N7002DW-X-F 1 SYS_PMU_ANALOG_AC_DET 1 Q1215 SYS_ACIN V5 R12032 SYS_AC_DET 25 SM-LF 2 5% 1/16W MF-LF 402 3 24 D LMC7211 V+ AC_ENABLE_L 10K 2N7002 SM-LF 1 Q1220 D LMC7211 R1224 1 5% 1/16W MF-LF 402 2 U1220 2 4 V+ 10K 5% 1/16W MF-LF 2 402 SYS_AC_DET_L U1200 R1216 10K 5% 1/16W MF-LF 2 402 20% 16V CERM 2 402 1% 1/16W MF-LF 402 2 R1215 10K 0.01uF 100K 1% 1/16W MF-LF 402 1 R1208 1 A29_DETECT 13 3 ANALOG_AC_DET 5% 1/16W MF-LF 1 402 1 M C 2 1 5% 1/16W MF-LF 2 402 20% 10V 2 CERM 402 1% 1/16W MF-LF 2 402 R1222 2 100K C1220 0.1uF 52.3K 1 AC_ENABLE_GATE 1 R1228 1 R1225 SYS_ADAPTER_ANA

C U89F 6 OF 10 VCC CORE 4 +VCCP C202 D 5 6 CRACK_GPIO MCHGND6 MCHGND4 2 5 CRACK_GPIO 3 4 1 6 MCHGND2 2 5 CRACK_GPIO 3 4 CRACK_GPIO 22,31 A MCHGND5 Wistron Corporation 21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C. 2N7002DW-7F-GP 2N7002DW-7F-GP Title CRESTLINE(5/6)-PWR/GND Size Document Number Custom Date: Friday, March 30, 2007 Rev PV NORN Sheet 12 of 51 5 U89I A13 A15 A17 A24 AA21 AA24 AA29 AB20 AB23 AB26 AB28 AB31 AC10 AC13 AC3 AC39 AC43 AC47 AD1 AD21 AD26 AD29 AD3 AD41 AD45 AD49 AD5 AD50 AD8 AE10 AE14 AE6 AF20 AF23 AF24 AF31 AG2 AG38 AG43 AG47 AG50 AH3 AH40 AH41 AH7 AH9 AJ11 AJ13 AJ21 AJ24 AJ29 AJ32 AJ43 AJ45 AJ49 AK20 AK21 AK26 AK28 AK31 AK51 AL1 AM11 AM13 AM3 AM4 AM41 AM45 AN1 AN38 AN39 AN43 AN5 AN7 AP4 AP48 AP50 AR11 AR2 AR39 AR44 AR47 AR7 AT10 AT14 AT41 AT49 AU1 AU23 AU29 AU3 AU36 AU49 AU51 AV39 AV48 AW1 AW12 AW16 D C 4 VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS V

402 R70 0 5% 1/16W MF 2 402 NO STUFF NO STUFF 1 1 R76 0 5% 1/16W MF 2 402 R78 0 5% 1/16W MF 2 402 R01D R00D R10D CPU_BTR 1 R84 0 5% 1/16W MF 2 402 NO STUFF NO STUFF 1 1 R88 0 5% 1/16W MF 2 402 R92 0 5% 1/16W MF 2 402 R01E R10E Q3 NO STUFF NO STUFF 1 1 R23 2N7002DW R31 0 R00E CPU_BTR R12 1 SOT-363 0 0 5% 1/16W MF 2 402 5% 1/16W MF 2 402 5% 1/16W MF 2 402 STUFF PASS TRANSISTOR ONLY IF R10E, R01E, OR PULLUP STUFFED CPU_PLL_FS01 1 R132 82K CPU_BST G +5V_SLEEP NOW REQUIRED FOR PLL_STOP_LR01A PULLUP TO ENSURE THAT Vgs OF PASS TRANSISTOR ON CPU_PLL_CFG<4> IS MET. CPU_BST CPU_PLL_CFG<0> CPU_PLL_CFG<1> CPU_PLL_CFG<2> CPU_PLL_CFG<3> CPU_PLL_CFG<4> 1 R68 S 10K 5% 1/16W MF 2 402 D 1 R50 2 1 R35 6 1 +3V_SLEEP 10K 3 5% 1/16W MF 2 402 7 D PLL_STOP_L 3 G S 29 7 2 Q13 2N7002 5 CPU_PLL_STOP_OC SOT-363 S 4 CPU_PLL_FS00 SM G CPU_BST Q3 2N7002DW D 1 6 Q14 2N7002DW D C 7 PLL_STOP_L Q14 2N7002DW 2 G SOT-363 S 1 3 SOT-363 CPU_PLL_FS10 D 29 7 CPU_PLL_STOP_OC 5 G CPU_PLL_STOP_BASE S

5% 1/16W MF 2 402 0 5% 1/16W MF 5% 1/16W MF 2 402 R10C R01D R00D NO STUFF NO STUFF 1 2 402 R13 0 1 1 R14 R15 0 5% 1/16W MF 2 402 R10D 0 2 402 R10E NO STUFF 1 R16 R18 0 5% 1/16W MF 1 0 5% 1/16W MF 5% 1/16W MF 2 402 NO STUFF R27 SOT-363 0 5% 1/16W MF 2 402 2N7002DW 1 R17 0 R00E Q1 NO STUFF 1 5% 1/16W MF 5% 1/16W MF 2 402 R01E NO STUFF NO STUFF 1 2 402 STUFF PASS TRANSISTOR ONLY IF R10E, R01E, OR PULLUP STUFFED 2 402 CPU_PLL_FS01 1 R48 82K 10K 5% 1/16W MF 402 2 5% 1/16W MF 2 402 47K 2 402 R01B R00B NO STUFF NO STUFF 1 G R00A R10A NO STUFF 1 CPU_PLL_CFG<0> 5 CPU_PLL_CFG<1> 5 CPU_PLL_CFG<2> 5 CPU_PLL_CFG<3> 5 CPU_PLL_CFG<4> 5 2 +5V_SLEEP NOW REQUIRED FOR PLL_STOP_L R01A PULLUP TO ENSURE THAT Vgs OF PASS NO STUFF TRANSISTOR ON CPU_PLL_CFG<4> IS MET. 1 R19 0 +3V_SLEEP +5V_SLEEP 5% 3 7 D PLL_STOP_L 3 D 1 G Q1 2N7002DW S 31 7 2 Q3 2N7002 CPU_PLL_STOP_OC CPU_PLL_FS00 SM 5 G SOT-363 S 4 6 D C Q2 7 PLL_STOP_L 2N7002DW 2 G SOT-363 S Q2 2N7002DW 1 3 SOT-363 CPU_PLL_FS10

1/16W MF 2 402 1 R25 R00C R10C NO STUFF 1 NO STUFF 1 R26 0 5% 1/16W MF 2 402 0 5% 1/16W MF 2 402 5% 1/16W MF 2 402 R13 0 R01D 1 R14 R10D NO STUFF 1 NO STUFF 1 R15 0 5% 1/16W MF 2 402 R00D R16 0 5% 1/16W MF 2 402 5% 1/16W MF 2 402 0 R01E R10E NO STUFF 1 1 2N7002DW R18 5% 1/16W MF 2 402 5 CPU_PLL_CFG<2> 5 CPU_PLL_CFG<3> 5 CPU_PLL_CFG<4> 5 R00E R27 0 5% 1/16W MF 2 402 STUFF PASS TRANSISTOR ONLY IF R10E, R01E, OR PULLUP STUFFED CPU_PLL_FS01 R48 10K 3 5% 1/16W MF 2 402 7 PLL_STOP_L D 3 NO STUFF Q1 D 1 G 2N7002DW S 30 7 CPU_PLL_STOP_OC Q3 5 G SOT-363 S 4 CPU_PLL_FS00 SM Q2 2N7002DW 7 PLL_STOP_L 2 2N7002DW SOT-363 G SOT-363 S 1 3 CPU_PLL_FS10 D 30 7 CPU_PLL_STOP_OC 5 G S CPU_PLL_STOP_BASE 3 R47 4 1 249K 2 Q4 1 STATE ENCODING 2N3904 1% 1/16W MF 402 34 30 M C 6 D Q2 SM LOW SPEED HIGH SPEED PLL DISABLE 2 CPU_PLL_STOP_OC 0.0X PLL OFF 0 1111 0F 1.0X 0 0011 03 2.0X 333 PLL BYPASS 267 0 0100 04 3.0X 500 400 0 1000 08 4.0X 667 533 0 1010 0A 5.0X 833 667 0 1011 0B 5.5X 917

MF-LF 2 402 R1209 1% 1/16W MF-LF 470K 1 402 2 R1202 97.6K C1200 1 R1204 1V20_REF 2 4 AC_DET_DIV 3 10K 1% 1/16W MF-LF 402 1 SYS_AC_DET 25 25 18 13 1 5 R12052 1M SYS_ACIN_L D SOT23-LF S R1227 1 4.7M 2 5% 1/16W MF-LF 402 R1226 127K 1% 1/16W MF-LF 2 402 13 C 2N7002DW-X-F 2 5 5% 1/16W MF-LF 402 1% 1/16W MF-LF 402 1 Q1208 A29_DET_L G 2 1 1% 1/16W MF-LF 2 402 4 1 V5 402K SOT-363 S 3 R1206 1 57.6K G 3 11 A29_DET_REF R1223 2N7002DW-X-F V- SYS_PMU_ANALOG_AC_DET 1 Q1215 SYS_ACIN 2 5% 1/16W MF-LF 402 3 24 D SM-LF 5 R12032 AC_ENABLE_L 10K 2N7002 SM-LF 1 Q1220 D LMC7211 R1224 1 5% 1/16W MF-LF 402 2 U1220 2 4 V+ 10K 5% 1/16W MF-LF 2 402 SYS_AC_DET_L LMC7211 V+ 10K 5% 1/16W MF-LF 2 402 U1200 R1216 A29_DETECT 13 3 ANALOG_AC_DET 5% 1/16W MF-LF 1 402 1 R1215 10K 20% 16V CERM 2 402 1% 1/16W MF-LF 402 2 14 R1208 1 0.01uF 100K 1% 1/16W MF-LF 402 1 1 5% 1/16W MF-LF 2 402 20% 10V 2 CERM 402 1% 1/16W MF-LF 2 402 R1222 2 100K C1220 0.1uF 52.3K 1 AC_ENABLE_GATE 1 R1228 1 R1225 SYS_ADAPTER_ANALOG_AC_DET 1 =PP3

-LF 402 R1513 16 13 12 11 PWRON_L 1 0 5% 1/16W MF-LF 402 A 2 4 B PP5V_ALL 6 1 e r C1581CRITICAL 0.01UF 20% Q1506 16V 2 2 Q1505_G 100K 1 2 1 2 5 Q1503_G 3 5% 1/16W MF-LF 402 6 B 4 RDSON=0.04 OHM @ VGS=2.5 V C1582 0.01UF 1 2 20% 16V CERM 402 Q1505 3 Q1504 6 2N7002DW-X-FD SOT23-LF S TSOP-LF R1508 2N7002 G Q1503 SI3446DV PP5V_ALL 3 D 1 C PEAK CURRENT 0.1A PP2V5_ALL 1 D y r PP2V5_ALL 5 2 G Q1504 D 2N7002DW-X-F SOT-363 SOT-363 S S 4 G 2 SYS_SLEEP 11 12 13 16 26 30 54 1 2.5V Vreg SYNC_MASTER=FINO-PC SYNC_DATE=06/20/2005 NOTICE OF PROPRIETARY PROPERTY THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR AGREES TO THE FOLLOWING I TO MAINTAIN THE DOCUMENT IN CONFIDENCE II NOT TO REPRODUCE OR COPY IT III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART SIZE APPLE COMPUTER INC. DRAWING NUMBER SCALE SHT NONE 8 7 6 5 4 3 2 REV. 051-6790 D 15 1 OF 19 154 A 8 6 7 2 3 4 5 1 D D y r PP5V_ALL PP12V_ALL 1 R16021 a n i C1600 0.01UF 20% 16V 2 CERM 402 3.6K 5% 1/16W M

2 R01E R10E NO STUFF 1 R18 0 5% 1/16W MF 2 402 5% 1/16W MF 2 402 1 5 CPU_PLL_CFG<3> 5 CPU_PLL_CFG<4> 5 NO STUFF R27 0 5% 1/16W MF 2 402 STUFF PASS TRANSISTOR ONLY IF R10E, R01E, OR PULLUP STUFFED CPU_PLL_FS01 R48 10K 3 5% 1/16W MF 2 402 7 D PLL_STOP_L 3 G 2N7002DW S 30 7 Q3 NO STUFF Q1 D 1 CPU_PLL_STOP_OC 5 G SOT-363 S 4 CPU_PLL_FS00 SM Q2 2N7002DW PLL_STOP_L 2 Q2 2N7002DW SOT-363 G SOT-363 S 1 3 CPU_PLL_FS10 D 30 7 CPU_PLL_STOP_OC 5 G S CPU_PLL_STOP_BASE 3 R47 4 1 249K 2 Q4 1 STATE ENCODING 2N3904 1% 1/16W MF 402 34 30 M C 6 D 7 SM LOW SPEED HIGH SPEED PLL DISABLE 2 CPU_PLL_STOP_OC 0 1 X N CPU CONFIGURATION B MAXBUS VSEL INVERTED HRESET_L MAXBUS_SLEEP CRITICAL BUSTYPE SELECT 1.5V INTERFACE 1_5V_MAXBUS R149 1_5V_MAXBUS 5 39 23 7 5 CPU_HRESET_L 0.0X PLL OFF 0 1111 0F 1.0X 0 0011 03 2.0X 333 PLL BYPASS 267 0 0100 04 3.0X 500 400 0 1000 08 4.0X 667 533 0 1010 0A 5.0X 833 667 0 1011 0B 5.5X 917 733 0 1001 09 6.0X 1000 800 0 1101 0D 6.5X 1083 867 0 0101 05 7.0X 1167 933 0 001

402_16V4Z~D FSC CLKSEL2 2 2 C13 0.047U_0402_16V7K~D 2 1 @ 1 +CK_VDD_REF C12 0.047U_0402_16V4Z~D 1 C11 4.7U_0603_6.3V4Z~D 1 2 @ R9 0_0402_5%~D 1 C9 0.1U_0402_16V4Z~D +CK_VDD_48 C3 0.1U_0402_16V4Z~D CLK_SCLK 2 C8 10U_0805_10V4Z~D 3 <27,38,48> CKG_SMBCLK Q1B 2N7002DW-T/R7_SOT363-6~D 4 1 MINI2CLK_REQ# 1 2 @ L2 BLM21PG600SN1D_0805~D +3.3V_M D +CK_VDD_MAIN2 2 C2 10U_0805_10V4Z~D CLK_SDATA Q1A 2N7002DW-T/R7_SOT363-6~D 1 R851 0_0805_5%~D 1 2 1 +CK_VDD_MAIN 1 2 L1 BK2125HS601-T 0805~D C1 0.1U_0402_16V4Z~D 6 <27,38,48> CKG_SMBDAT R2 2.2K_0402_5%~D 1 2 @ R3 0_0402_5%~D R1 2.2K_0402_5%~D 1 +3.3V_M 1 2 +CK_VDD_MAIN 1 R49 1 R52 SATA_CLKREQ#_R 1 R53 CLK_MCH_3GPLL <10> CLK_3GPLLREQ# <10> CLK_PCIE_SATA <23> SATA_CLKREQ# <24> A DELL CONFIDENTIAL/PROPRIETARY SLG8LP554VTR_QFN72_10X10~D Compal Electronics, Inc. PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT BE TRANSFERR

TA PP5V_S0_IDE_PATA 6 MAKE_BASE=TRUE VOLTAGE=5V MIN_LINE_WIDTH=0.35MM MIN_NECK_WIDTH=0.25MM 5 4 2 1 R3865 1 6.2K 5% 1/16W MF-LF 2 402 =PP3V3_S0_SB 64 25 22 ODD_PWR_EN_SLOW_START_L R3876 1 C3876 3 ODD_PWR_EN_SLOW_START C 1 Q3875 SB_GPIO5 ODD_PWR_EN_L 26 22 2N7002DW-X-F 2 G SOT-363 S MAKE_BASE=TRUE NOSTUFF 2 2 10K G R3851 C3875 5% 1/16W MF-LF Per ATA Spec 2 402 0.47UF 10% 2 6.3V CERM-X5R 402 1 R3877 23 100K 21 5% 1/16W MF-LF 2 402 21 21 1 21 21 21 21 ODD detect need less than 100ms include OS latency 21 21 21 OUT 21 OUT NC NC IDE_RESET_L IDE_PDD<7> IDE_PDD<6> IDE_PDD<5> IDE_PDD<4> IDE_PDD<3> IDE_PDD<2> IDE_PDD<1> IDE_PDD<0> IDE_PDIOW_L IDE_PDIORDY IDE_IRQ14 21 21 NO STUFF 21 C3804 1 1 M-ST-SM IDE_PDA<1> IDE_PDA<0> IDE_PDCS1_L 10pF NC 33K 2 1 NC 5% 1/16W MF-LF 2 402 4 3 6 5 8 7 10 9 12 11 14 13 16 15 18 17 20 19 22 21 24 23 26 25 28 27 30 29 32 31 34 33 36 35 NC 38 37 40 39 42 41 44 43 46 45 48 47 50 49 5% 50V CERM 2 402 IDE_CSEL_PD R3853 51 4.7K SOT-363 S CRITICAL J3801 5-1775184-0 1 2N7002DW

A_DEEP_IDLE_R R824 2 @ R676 10K_0402_5% VGA@ 1 10K_0402_5% 091026 add R824 10K PU to +3VSDGPU B DGPU_PWR_EN 091022 follow NV OPTIMUS D.G. Q47A 1 SMB_EC_CK2_R 2 27MHZ_20P_7A27000010 VGA@ C739 27P_0402_50V8J VGA@ DGPU_PWR_EN <13,31,35> 6 EC_SMB_CK2 <5,9,31> 2N7002DW-T/R7_SOT363-6 OPT@ OPT@ Q47B 4 SMB_EC_DA2_R 3 EC_SMB_DA2 <5,9,31> 5 L27 MBK1608121YZF_0603 2 2 MBK1608121YZF_0603 MBK1608121YZF_0603 VGA_LVDS_SCL_C L31 1 2 VGA_LVDS_SDA_C 1 2 L30 DIS@ MBK1608121YZF_0603 1 1 C737 C738 DIS@ DIS@ VGA_DDCCLK_C VGA_DDCDATA_C 091124 change C740/C739 to 27PF R1490 100K_0402_5% VGA@ PLTRST_VGA# DIS@ 1 1 L28 VGA_DDCCLK <15> VGA_DDCDATA <15> DIS@ DIS@ 100P_0402_50V8J 2 VGA_LVDS_SCL <14> VGA_LVDS_SDA <14> C748 DIS@ 1 2 C747 DIS@ 12P_0402_50V8J 1 091124 change crystal Y5 P/N to SJ127P0M800 12P_0402_50V8J P G 100112 change Q47 P/N from SB00000AR00 to SB00000DH00 PLTRST_VGA# 4 2 C35 P8 0.9V GPIO14 C29 A DGPU_HOLD_RST# Deep P12 MEM_VREF SLI_SYNC PWR_LEVEL MEM_VID 12P_0402_50V8J 2 0_0402_5% 0.8V 0.85V GPIO10 GPIO11 GPI